# **BAB III**

# **METODE PENELITIAN**

# 3.1 Tahapan Penelitian

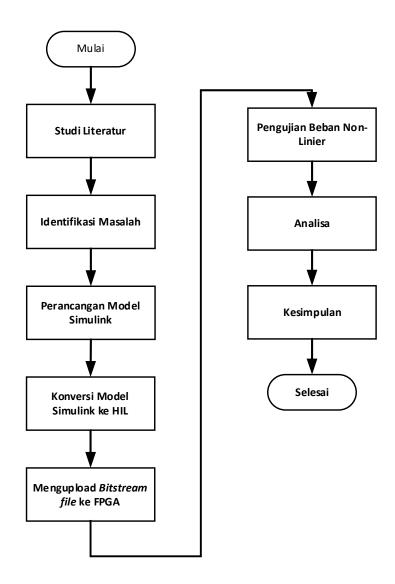

Diagram alur penelitian diperlukan dalam sebuah penelitian agar mudah dipahami dan dapat menjadi pedoman selama prosesnya. Diagram alur tahapan penelitian ini disajikan pada Gambar 3. 1.

Gambar 3. 1 Diagram alur penelitian

Dalam proses perancangan dan pembuatan sistem terdiri dari beberapa tahapan, antara lain:

- Tahap kesatu adalah memulai penelitian. Ini merupakan tahap awal dari penelitian.

- 2. Tahap kedua adalah studi literatur. Tahap ini meliputi proses pengumpulan referensi dan pembelajaran teori dasar mengenai berbagai topik, yaitu harmonisa, filter aktif, perhitungan arus referensi, Model Predictive Control (MPC), beban, daya listrik, FPGA Zedboard, MATLAB, Simulink, dan Fixed-Point. Tujuan utamanya adalah untuk memperoleh pemahaman yang lebih komprehensif mengenai konsep teoretis dan aplikasi praktis penelitian yang akan dilakukan. Referensi dikumpulkan dari beragam sumber, termasuk jurnal penelitian nasional dan internasional, e-book, serta situs web. Selain pendalaman teori yang telah disebutkan, pada tahap ini juga dilakukan kajian terhadap komponen-komponen pada FPGA Zedboard, MATLAB, dan Simulink yang akan digunakan dalam penelitian. Kajian komponen ini mencakup proses pemilihan komponen, penentuan jenis komponen, hingga penetapan besaran nilainya.

- 3. Tahap ketiga adalah identifikasi masalah. Setelah studi literatur dilaksanakan, identifikasi masalah bertujuan untuk mendefinisikan ruang lingkup dan tujuan penelitian.

- 4. Tahap keempat adalah perancangan model Simulink Tahap ini meliputi perancangan pemodelan dan program kendali yang akan disimulasikan pada MATLAB Simulink di PC *host*. Pada tahap ini juga dilakukan perancangan berbagai komponen, meliputi: model untuk rangkaian jaringan listrik tiga fasa empat kawat; rangkaian ekstraksi harmonisa guna menghasilkan nilai

- arus referensi; serta rangkaian konverter tiga fasa empat kawat beserta program kendali MPC (Model Predictive Control).

- 5. Tahap kelima adalah Konversi Model Simulink Ke HIL, setelah model simulink dirancang kemudian model MPC akan dikonversikan ke bentuk *Bitstream File*, yang file tersebut akan di*upload* ke FPGA.

- 6. Tahap keenam adalah meng*upload* file *bitstream* yang telah di*generate* oleh FIL Wizard, ke FPGA Zedboard menggunakan Aplikasi Vivado.

- 7. Tahap ketujuh adalah pengujian HIL menggunakan beban non-linier menggunakan simulator HIL.

- 8. Tahap kedelapan adalah analisis hasil pengujian HIL dengan simulator Simulink.

- 9. Tahap kesepuluh adalah membuat kesimpulan dari data yang dihasilkan.

- 10. Tahap kesebelas adalah penyelesaian penelitian. Pada tahap ini, semua tahapan yang diperlukan dalam penelitian telah dilaksanakan sesuai prosedur.

# 3.2 Blok Diagram Sistem

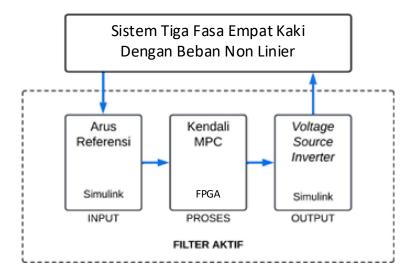

Penelitian ini merancang pengendali konverter untuk filter aktif. Jenis filter aktif yang akan dibuat adalah filter aktif *shunt* karena paling populer serta memiliki topologi dan prosedur instalasi yang sudah dipahami dengan baik. Prinsip dasar filter aktif *shunt* adalah membangkitkan arus kompensasi guna meredam harmonisa, sehingga arus sumber mendekati bentuk sinusoidal.

Gambar 3. 2 Blok Diagram Sistem

Pada Gambar 3. 2 menunjukan blok diagram dari sistem filter aktif *shunt*. Dari blok diagram tersebut, terdapat tiga tahapan pada pada sistem untuk mereduksi harmonisa yang terdapat pada jaringan listrik. Tahapan tersebut yaitu:

# a. Input

Perhitungan arus referensi, yang dilakukan pada bagian input, menggunakan teori *Synchronous Reference Frame* (SRF). Hasil perhitungan ini selanjutnya akan digunakan untuk kalkulasi pada kontroler sistem.

### b. Proses

Pada bagian proses merupakan bagian kendali pensaklaran konverter, metode *Model Predictive Control* (MPC) merupakan metode yang digunakan untuk kendali pensaklaran konverter. Kontroler mengatur pensaklaran konverter dengan menggunakan arus referensi sebagai referensi agar konverter dapat menghasilkan arus filter sesuai dengan arus referensi yang diberikan.

# c. Output

Bagian output ini merupakan bagian dimana konverter melakukan pensaklaran dan menghasilkan arus filter sesuai dengan instruksi dari kontroler.

Voltage source inverter merupakan jenis konverter yang digunakan. arus akan dimasukan kedalam sistem melalui filter RL oleh konverter sesuai dengan arus referensi yang diinputkan.

# 3.3 Algoritma MPC pada Filter Aktif

Gambar 3. 3 Algoritma MPC pada Filter Aktif

Pada Gambar 3. 3 menunjukkan diagram alir algoritma *model predictive* control (MPC) untuk inverter tiga fasa sumber tegangan pada filter aktif. Diagram alir ini dijelaskan sebagai berikut:

- 1. Tahap pertama dari alir algoritma ini adalah mengukur nilai arus keluaran filter i(k) dan menentukan arus referensi  $i^*(k)$ . Selanjutnya nilai tersebut dijadikan sebagai inputan yang kemudian masuk pada model prediksi.

- Selanjutnya Algoritma akan menginisialisasi iterasi (x) dan cost function

(g) menjadi nol dan tak terhingga.

- 3. Algoritma masuk ke *loop*, kemudian iterasi *for loop* dihitung setiap selesainya satu siklus pada *for loop*.

- 4. Kemudian menentukan nilai arus haisl prediksi  $i^p(k+1)$ .

- 5. Hasil dari perdiksi arus dihungung error-nya terhadap referensi menggunakan fungsi biaya g.

- 6. Pada saat looping, jika  $g < g_{opt}$ , nilai g terkecil disimpan dan digunakan untuk mengganti nilai  $g_{opt}$ . Selain menyimpan cost function nilai iterasi optimal  $x_{opt}$  tersebut ikut disimpan karena menggambarkan kombinasi swiching state.

- 7. Kombinasi *switching state* juga merupakan iterasi x yang terus dilakukan hingga muncul 8 iterasi sesuai  $x \ge 8$ , setelah 8 iterasi nilai numerik dalam  $x_{opt}$  diteruskan ke algoritma.

- 8. Sinyal *switching* untuk konverter tersebut dipilih  $x_{opt}$  yang disimpulkan dari daftar status *switching state* yang telah ditentukan.

- 9. Status switching kemudian diterapkan ke konverter, yang mengubah tegangan dan arus. Setelah itu, kembali ke langkah pertama. Rantai proses MPC pada bagian inverter dilakukan secara terus menerus sepanjang pengoperasian sistem.

# Sumber 3 fasa isb isb isc Non Linier Reference Current Generation VS 3 d 3 leg Sb Cost Function Model MPC FILTER AKTIF

# 3.4 Blok Diagram Filter Aktif dengan kendali MPC

Gambar 3. 4 Blok Diagram Filter Aktif dengan Kendali MPC

Berdasarkan diagram blok sistem pada Gambar 3. 4, terdapat jaringan listrik tiga fasa yang menyuplai beban non linier. Dalam sistem ini, nilai tegangan sumber Vs nilai arus beban  $i_{La}$ ,  $i_{Lb}$ , dan  $i_{Lc}$  digunakan untuk menghitung arus referensi  $i^*$ . Nilai arus filter  $i_{fa}$ ,  $i_{fb}$ , dan  $i_{fc}$  digunakan untuk menghitung arus prediksi  $i^p$  dalam sistem kendali MPC.

Langkah selanjutnya adalah mencari selisih antara nilai prediksi arus **i**<sup>p</sup> dan arus referensi **i**\*, yang dilakukan pada blok *Cost Function Minimation*. Pada proses ini dicari nilai *cost function* dengan nilai error terkecil untuk memilih kondisi switching **S**<sub>a</sub>, **S**<sub>b</sub>, dan **S**<sub>c</sub> pada inverter untuk melakukan switching dan menghasilkan arus kompensasi sesuai dengan arus referensi i\* yang diinputkan.

Arus yang dihasilkan inverter **i**<sub>fa</sub>, **i**<sub>fb</sub>, dan **i**<sub>fc</sub> kemudian diumpankan kembali ke sistem jaringan tiga fasa untuk mereduksi harmonisa pada jaringan, sehingga bentuk gelombang arus sumber **i**<sub>fa</sub>, **i**<sub>fb</sub>, dan **i**<sub>fc</sub> dapat mendekati sinusoidal.

# 3.5 Pengujian Model

Dalam pengujian model, ada beberapa skenario yang akan dilaksanakan untuk menguji Model yang telah dibuat.

# a. Skenario pertama

Model akan diuji dengan menggunakan beban non linier yang seimbang pada setiap fasanya.

### b. Skenario kedua

Model akan diuji dengan menggunakan beban non linier yang tidak seimbang pada fasa b dan fasa a dan fasa c nilai bebannya sama.

# c. Skenario ketiga

Model akan diuji dengan menggunakan beban non linier yang tidak seimbang pada fasa c dan fasa a dan fasa b nilai bebannya sama.

# d. Skenario keempat

Model akan diuji dengan menggunakan beban non linier yang tidak seimbang pada fasa a dan fasa b dan fasa c nilai bebannya sama.

Keempat skenario tersebut akan diterapkan pada HIL untuk dianalisis nilai THD arusnya, guna menentukan apakah sudah sesuai standar atau belum.

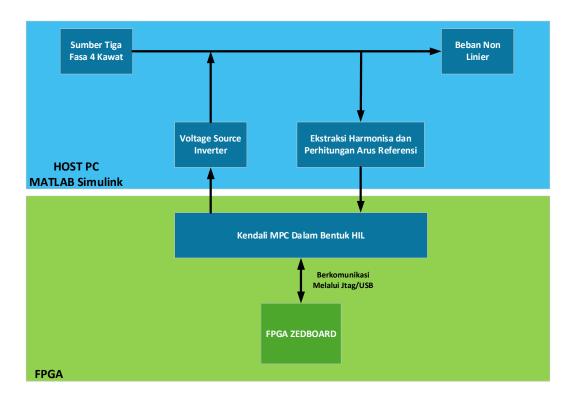

# 3.6 Simulasi Hardware in the loop

Salah satu teknik simulasi adalah *Hardware-in-the-loop* (HIL). Teknik HIL ini merupakan metode yang menggabungkan Simulink dengan perangkat keras FPGA. Dalam aplikasinya, teknik HIL memanfaatkan FPGA Zedboard sebagai kontroler dari sistem yang dirancang. Penggunaan teknik HIL dapat membantu dalam perancangan sistem sehingga hasil yang diperoleh lebih valid karena

melibatkan perangkat keras secara langsung dalam proses simulasi. Pada penelitian ini, rangkaian kendali MPC (Model Predictive Control) diimplementasikan pada perangkat FPGA Zedboard. Gambaran umum mengenai topologi simulasi HIL yang digunakan dalam penelitian ini disajikan pada Gambar 3. 5.

Gambar 3. 5 Diagram Kerja HIL

Pada tahap pertama, sistem jaringan listrik tiga fasa dengan proses ekstraksi harmonik dan perhitungan nilai arus acuan dimodelkan pada MATLAB/Simulink. Selanjutnya dibuat model pengontrol MPC menggunakan Simulink. Setelah dibuat sebagai model simulink, model pengontrol MPC disajikan sebagai blok *subsystem* yang kemudian mengunakan fasilitas *Vitis Model Composer blok* untuk mengatur bagian subsistem mana yang akan diatur pada FPGA, kemudian melakukan perhitungan matematis untuk menghasilkan model pensaklaran sinyal gating pada konverter untuk menghasilkan arus kompensasi yang sama dengan nilai arus referensi yang diberikan. Keluaran FPGA yang berupa sinyal pemilihan

pensaklaran harus diimplementasikan pada rangkaian konverter, dimana konverter tersebut diimplementasikan sebagai model simulink dan berjalan di*PC HOST*.

# 3.7 Peralatan Perancangan

Peralatan perancangan yang digunakan baik *hardware* maupun *software* adalah sebagai berikut:

- 1. PC dengan OS Windows 11, prosesor Amd Ryzen 7 5700x, RAM 48GB

- 2. *Software* MATLAB/Simulink 2022

- 3. Vitis Model Composer

- 4. Vivado

- 5. FPGA Zedboard